Today in #RISCV:

Register mtval (optionally) holds the fault address of a data fault, is specified to hold “all valid virtual addresses and the value zero. It need not be capable of holding all possible invalid addresses.”

Hit an invalid virtual address? Good luck debugging it.

Easy RISC-V Provides an Interactive Way to Explore the RISC-V Architecture

#CVUTFEL ( #CVUT FEE) Advanced Computer Architecture ( #comparch) course recodings of the first five lectures are published at #VHSky.cz. Czech language recordings from the 2021 round are available as well. The B4M35PAP course builds on the knowledge from the introductory #comparch B35APO course (recordings). Each student builds their own CPU design (tools and ISA are open). The #QtRvSim #RISCV educational simulator is provided for inspiration (online version and The Czech Technical University #comparch related courses guidepost https://comparch.edu.cvut.cz/).

P.S.: Help with tooling for transcribing the lectures in my Czenglish dialect into English subtitles would be appreciated, as well as all other forms of feedback. For the introductory course, we provide reusable LaTeX sources (CC-BY-SA license) that are open to pull requests.

Now that major distros have released upgrades, it's time to ask again:

I'm looking for a RISC-V board that works with Debian 13 or Ubuntu 25.10.

-really supported by the distro in question, not by some random downstream fork.

-installable via USB, not through some custom unobtainium cable.

-with display support, at a decent enough performance to be usable as a 1080p desktop.

Barebones RISC-V OS written in Zig / Timmy Xiao

Banana Pi BPI-CM6 design with SpacemiT K1 8 core RISC-V chip, CPU integrates 2.0 TOPs AI computing power. 8/16G DDR and 8/16/32/128G eMMC. support DeepX AI. will comming soon.

https://docs.banana-pi.org/en/BPI-CM6/BananaPi_BPI-CM6

#riscv #EdgeComputing #bananapi #raspberrypi #deepx #AI

We've updated to OpenSSL 3.6.0 and Tor 0.4.8.19 on our RISC-V Tor exit relay, which runs on the SiFive HiFive P550 board

To make the update/ rebuild process easier, we made a shell script that automatically builds OpenSSL and Tor from source, and it's free to use:

Upside of using #bevy and open source tooling in general is you can get your games to compile on non corporate approved architectures. I just got the #aarch64 and #RISCV builds running. (I can’t promise RISC-V works on real hardware yet as I don’t have any real hardware to test it.) If you have RISC-V hardware and want to test let me know. Here is the game running natively on a Pine Book Pro. #GameDev

idk why there are very loud proponents of open source who give up and even start throwing out their "realist" slaps n punches in regards to 'blobby' hardware (like how blobless cores n such basically shouldn't or can't be expected to exist ever—bad for business, unrealistic, whatevs else).

is blobless/oss hardware really so outlandish? :3

@kernellogger what are the pro's of an open source #cpu isa?

Like Ethernet and USB, RISC-V is not tied to the fortunes of any one company, so it is a more prudent bet for a company’s software ecosystem development for the long haul. This long-term safety is another reason the EU and NASA picked RISC-V for their future plans.

#riscV

https://riscv.org/blog/2023/03/top-ten-fallacies-about-risc-v/

""WE ARE NOT PREEMPTIVELY SUPPORTING BIG-ENDIAN ON RISC-V""

Linus send that to #LKML a few hours agom, after somebody asked if some of the big-endian work will make it into #Linux 6.18.

For the full thread, see: https://lore.kernel.org/lkml/CAHk-%3DwgYcOiFvsJzFb%2BHfB4n6Wj6zM5H5EghUMfpXSCzyQVSfA@mail.gmail.com/t/#mce138059dc56014643bbda330810183031ef5c06

There he calls the reasons documented on riscv.org as "craziness" and insane:

""In other words, it is suggesting that RISC-V add a big-endian mode due to

(a) internet protocols - where byte swapping is not an issue

(b) using "some RISC-V implementations don't do the existing Zbb extension" as an excuse

This is plain insanity. First off, even if byte swapping was a real cost for networking - it's not, the real costs tend to be all in memory subsystems - just implement the damn Zbb extension.""

Nice! :

“Writing An Operating System Kernel From Scratch”, Uros Popovic (https://popovicu.com/posts/writing-an-operating-system-kernel-from-scratch/).

Via HN: https://news.ycombinator.com/item?id=45240682

On Lobsters: https://lobste.rs/s/aokjpu/writing_operating_system_kernel_from

One week unit @TexasLinuxFest and I'm super excited! Not only am I speaking, but I'm helping to run the booth for the Austin RISC-V Group to show a bunch of demos and answer your questions. If you're in Austin please come by! This is one of my favorite local events, and I'm always proud to support and participate every year. If you don't want to hear from me, check out the speaker line-up, there are a lot of great talks: https://2025.texaslinuxfest.org/ #Austin #Linux #RISCV

Preview of coming attractions...

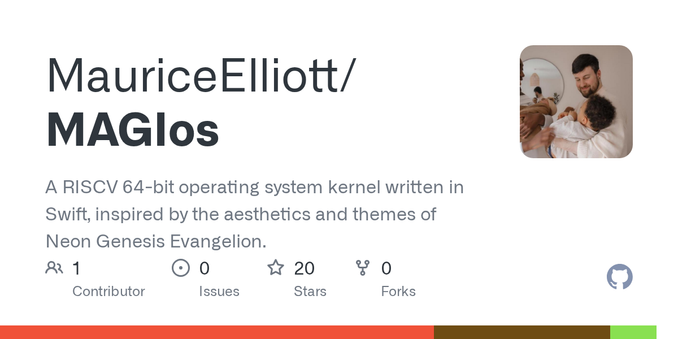

That brings us up to now where I’ve deleted the entire project on 3 separate occasions, switched between 3 processor architectures and considered a 4th (#arm was considered briefly) used way more #AI than I should have, eventually adopting a 0 to minimal approach because it kept fucking it up.

Now we’re here. Beautiful #swift kernel. #RISCV architecture. As much as is needed to just get a simple boot message out. We may continue on into uncharted territory!

Wish me luck!

The journey its taken to get here is long and winding.

I original did it in 32 bit with a C kernel intermediary. Then hated that, so tried switching to #odinlang, which was really nice, but had better support for 64 bit so I switched to that. I then found the multi boot header overly complicated, so switched to #RISCV. I then realised I just wanted to work in #swift so switched back to swift but this time in 64 bit. I then decided I’d learnt too much from reading riscv docs, so switched back.

New 33€ widescreen RISC-V machine has arrived (with an F133 Allwinner D1-based single core RV64 SoC and 1 GB of RAM)...

Write your own Rust-based RISC-V hypervisor in 1000 lines of code by Seiya Nuta:

https://1000hv.seiya.me/en/

https://github.com/nuta/hypervisor-in-1000-lines

Seya also published a guide to write a C-based RISC-V OS in 1000 LoC:

https://github.com/nuta/operating-system-in-1000-lines